home

site news

atari news

atari glossary

atari history

atari video game systems

> atari 2600

> atari 5200

> atari 7800

> atari lynx

> atari jaguar 64

> technical specs

> really 64bits?

> pcb-layout

> cartridge tech

> hardware

> software

> collection

> gallery

> 'panther'

project

> jaguar 2

> cojag

> kiddie rides

> 'do the math'

> atari jaguar CD

> atari xegs

atari computers

atari coin-op

atari stand-alone-systems

atari library

atari theater

atari links

legal stuff/imprint

contact us |

|

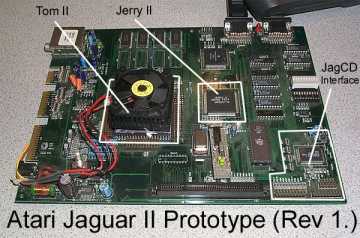

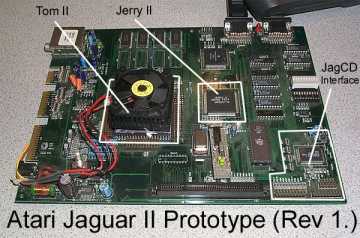

The 'Jaguar II' prototype

This

is the 'Jaguar II' prototype PCB. You'll notice, there is a second

DRAM-bank on the board; but it's empty...

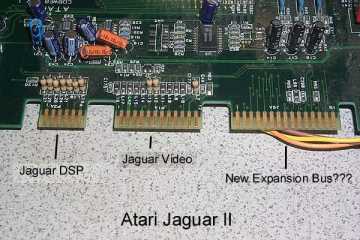

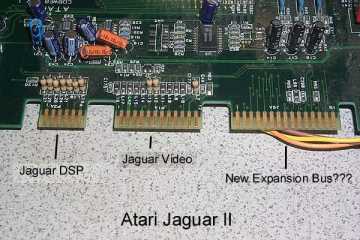

These are the

expansion-ports of the 'Jaguar II'. What is / was the new expansion-bus

for?

Those are (were) the

possible 'Jaguar II' system-specs. They were stated in a german

online-magazine in 1995. The editors claimed, that they received these

specs from Atari-internal sources they were not able to reveal.

So

let's consider these as speculative, but not unrealistic:

|

Size: |

10.5" x 12" x 3.5" |

|

Controls: |

Power on/off |

|

Display: |

Resolution up to

1600 x 600 pixels (50 Hz/interlace)

32-bit 'Extended True Color' display with 16,777,216 colors

simultaneously (additional 8 bits of supplimental graphics data

support possible)

Multiple-resolution, multiple-color depth objects (monochrome, 2-bit,

4-bit, 8-bit, 16-bit, 24-bit) can be used simultaneously |

|

Ports: |

Cartridge slot/expansion

port (64 bits)

RF video output

Video edge connector (video/audio output) (supports NTSC and PAL;

provides S-Video, Composite, RGB outputs, accessible by optional

add-on connector)

Four controller ports

Digital Signal Processor port (includes high-speed synchronous serial

input/output) |

|

Controllers: |

Eight-directional

joypad, size 5" x 4.5" x 1.5", cord 7 feet, six fire buttons (A, B, C,

D, E, F), pause and Option buttons, 12-key keypad (accepts

game-specific overlays) |

| |

|

| |

|

|

'Tom' (including

processors 1-5), 1,250,000 transistors, 292 pins |

|

Graphics Processing

Unit (processor #1) |

64-bit RISC

architecture (64 / 128 register processor)

64 registers of 128 bits wide (shadow-buffering)

Has access to all 2 x 64 bits of the system bus

Can read 128 bits of data in one instruction

Rated at 127.902 MIPS (million instructions per second)

Runs at 63.951 MHz

2 x 32K bytes of zero wait-state internal SRAM (matrix)

Performs a wide range of high-speed graphic effects

Programmable |

|

Object processor (processor

#2) |

64-bit RISC

architecture

Programmable processor that can act as a variety of different video

architectures, such as a sprite engine, a pixel-mapped display, a

character-mapped system, and others. |

|

Blitter (processor

#3) |

64 bits read and

write at the same time! (multibuffering)

8K read buffer (fifo)

8K write buffer (lifo)

Performs high-speed logical operations

Hardware support for Z-buffering and Gouraud shading |

|

Texture Mapping

Engine (processor #4) |

64-bit RISC

256K 'texture-work-ram' of zero wait-state internal CACHE

capable of doing about 900000 texture-mapped polyons,

without textures there can do 2500000 polyons.

realtime Gouraud and Phong shading |

|

J/MPEG 'COMBI' Chip

(processor #5) |

64 bits

not programmable

8K own data rom (with sinus) table

128K CACHE (fifo)

realtime J/MPEG decompression via CACHE (fifo)

DRAM memory controller

4 x 64 bits

Accesses the DRAM directly |

| |

|

| |

|

|

'Jerry',

900,000 transistors, 196 pins |

|

|

Digital Signal

Processor (processor #6) |

32 bits (32-bit

registers)

Rated at 53,3 MIPS (million instructions per second)

Runs at 53.3 MHz

Same RISC core as the Graphics Processing Unit

Not limited to sound generation

96K bytes of zero wait-state internal SRAM

CD-quality sound (16-bit stereo 50KHz)

Number of sound channels limited by software (minimum 16)

Two DACs (stereo) convert digital data to analog sound signals

Full stereo capabilities

Wavetable synthesis, FM synthesis, FM Sample synthesis, and AM

synthesis

A clock control block, incorporating timers, and a UART |

|

Motorola 68EC020 (processor

#7) |

Runs at 26.590MHz

perfect 68000 emulation

General purpose control processor |

Communication is performed with a high speed 64-bit data bus, rated at

2400 megabits / second. The 68000 is only able to access 16 bits of this

bus at a time.

The

'Jaguar II' contains eight megabytes (64 megabits) of fast page-mode DRAM, in

eight chips with 1024 K each.

The

'Jaguar II' would have had seven processors, which are contained in three

chips. Two of the chips are proprietary designs, nicknamed 'Tom' and

'Jerry'. The third chip is a standard Motorola 68EC020, used as a

coprocessor. 'Tom' and 'Jerry' are built using an 0.3 micron silicon

process. With proper programming, all seven processors can run in

parallel.

These two pictures were

taken at the 1995 Summer CES in Chicago: Sam Tramiel carrying a 'JagDuo'

(a combination of the Jaguar and the CD add-on), or possibly the 'Jaguar

II'.

This

may have been the case for the 'Jaguar II' or probably the 'JagDuo' (a

combination of the Jaguar and the CD add-on).

|